MIPS指令

操作码的长度决定了可以提供多少个指令数;操作码的编码一定要有唯一的解释

一、计算机的寻址方式

- 立即寻址:指令中给出操作数

- 直接寻址:指令中给出操作数所在的有效地址

- 间接寻址:指令中给出一个间接地址,间接地址在内存中寻找直接地址,直接地址读出操作数

- 寄存器间接寻址:指令给出寄存器编号,根据寄存器内容找出操作数

- 基址寻址:指令中给出一个寄存器编号,同时给出一个偏移地址,基址寄存器内容+偏移地址从内存中取操作数

二、操作码编码

- 定长操作码编码

- 扩展操作码编码

三、MIPS的指令可以分为3种操作类型

- R型

- I型

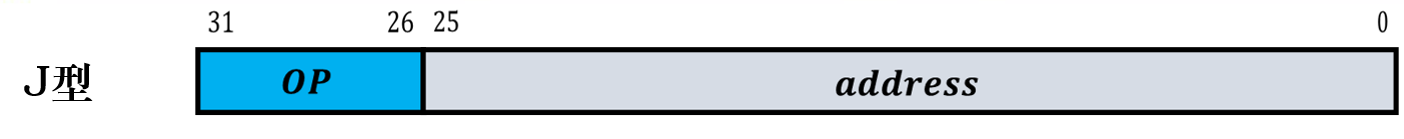

- J型

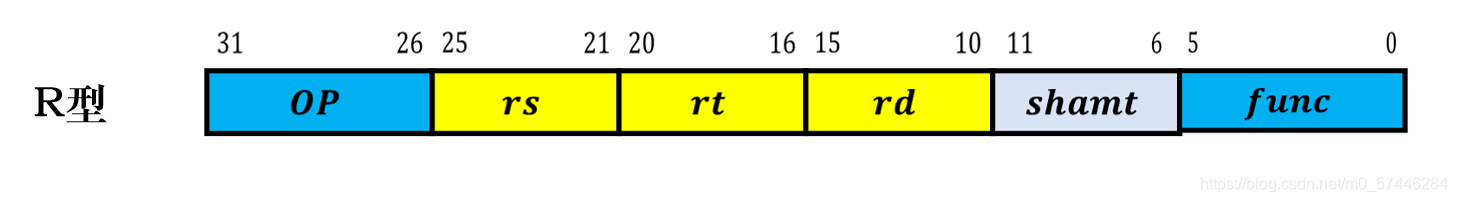

1、R型指令

- OP:000000 由func来决定他的功能

- rs、rt是两个源操作数所在的寄存器号

- rd是目的操作数所在的寄存器号

- shamt是位移量,执行移位操作的时候指明需要移动的次数

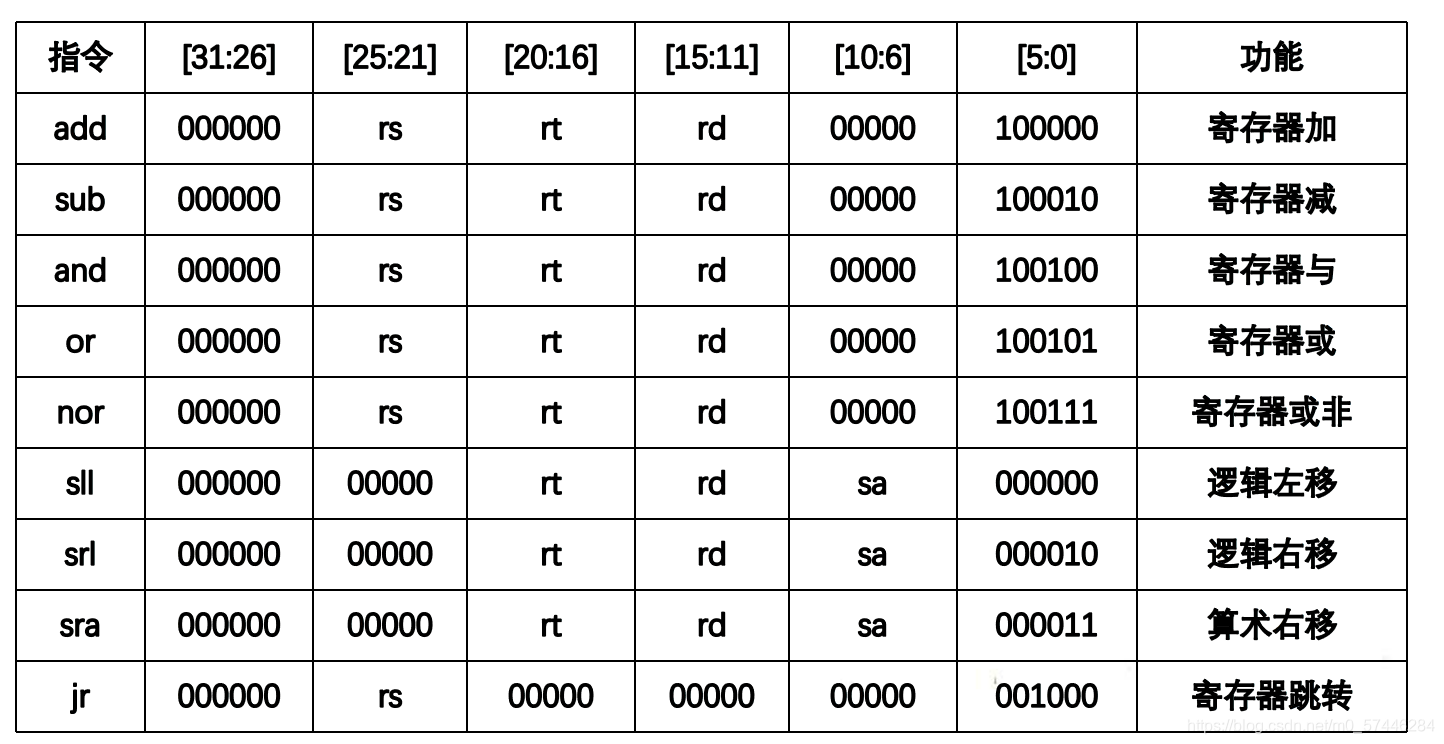

同时也要牢记R型指令的指令表:

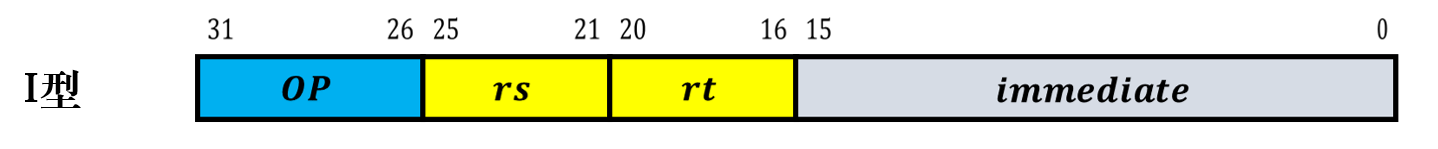

2、I型指令

- 操作功能由OP决定

- rs是第一个源操作数,immediate是第二个源操作数

- rt是目的操作数所在的寄存器编号

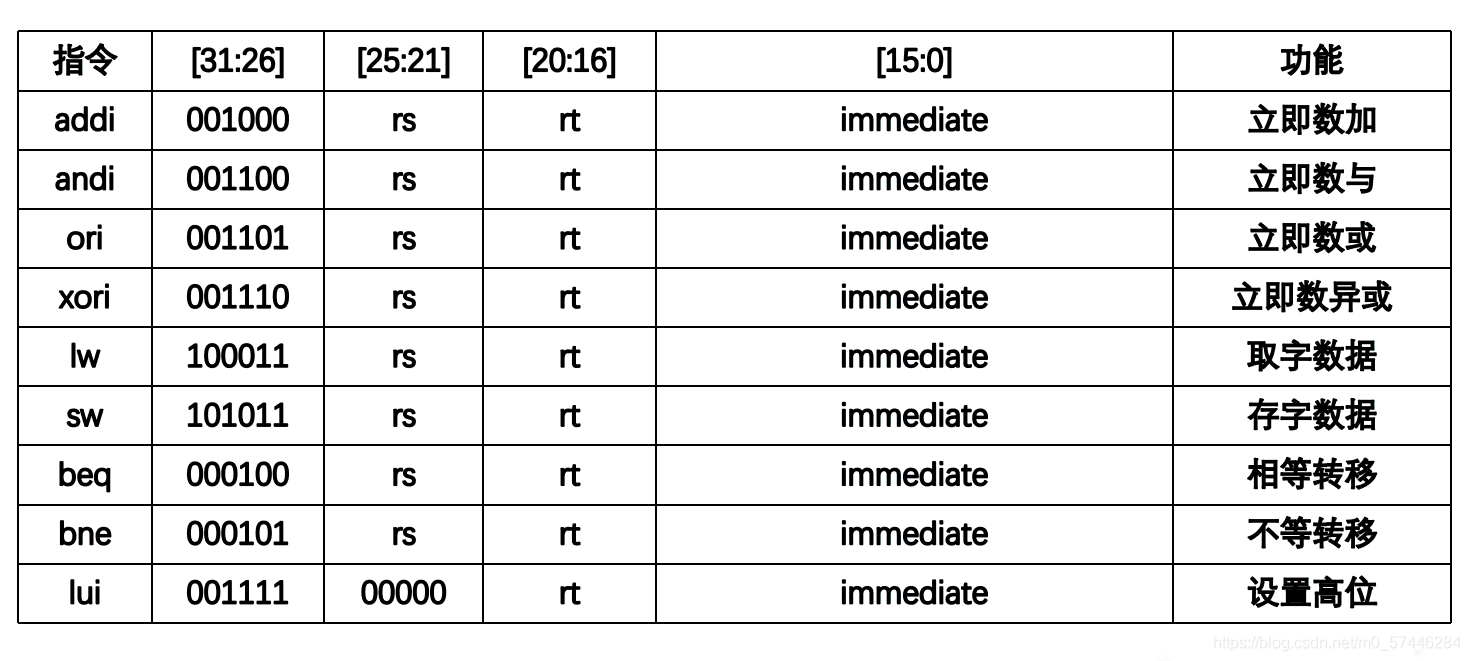

I型指令的操作表:

- 在I型指令中,addi指令是需要进行符号位扩展,但是andi、ori、xori指令只需要进行零扩展即可

- sw、lw、beq、bne等操作都是进行符号位扩展

3、J型指令

- 操作功能由OP决定

- 转移地址:26位(立即数)

J型指令操作表:

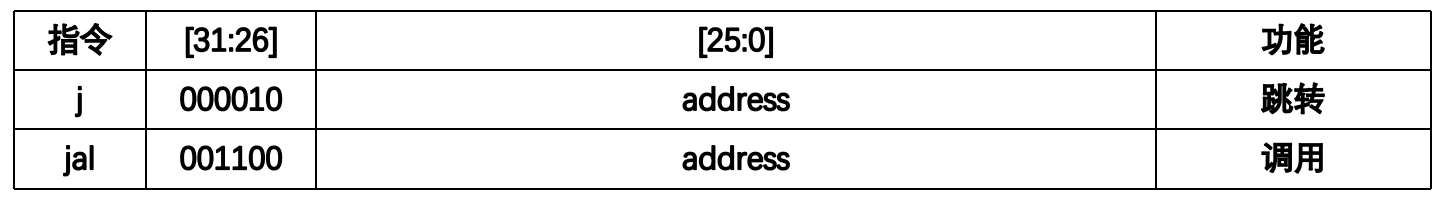

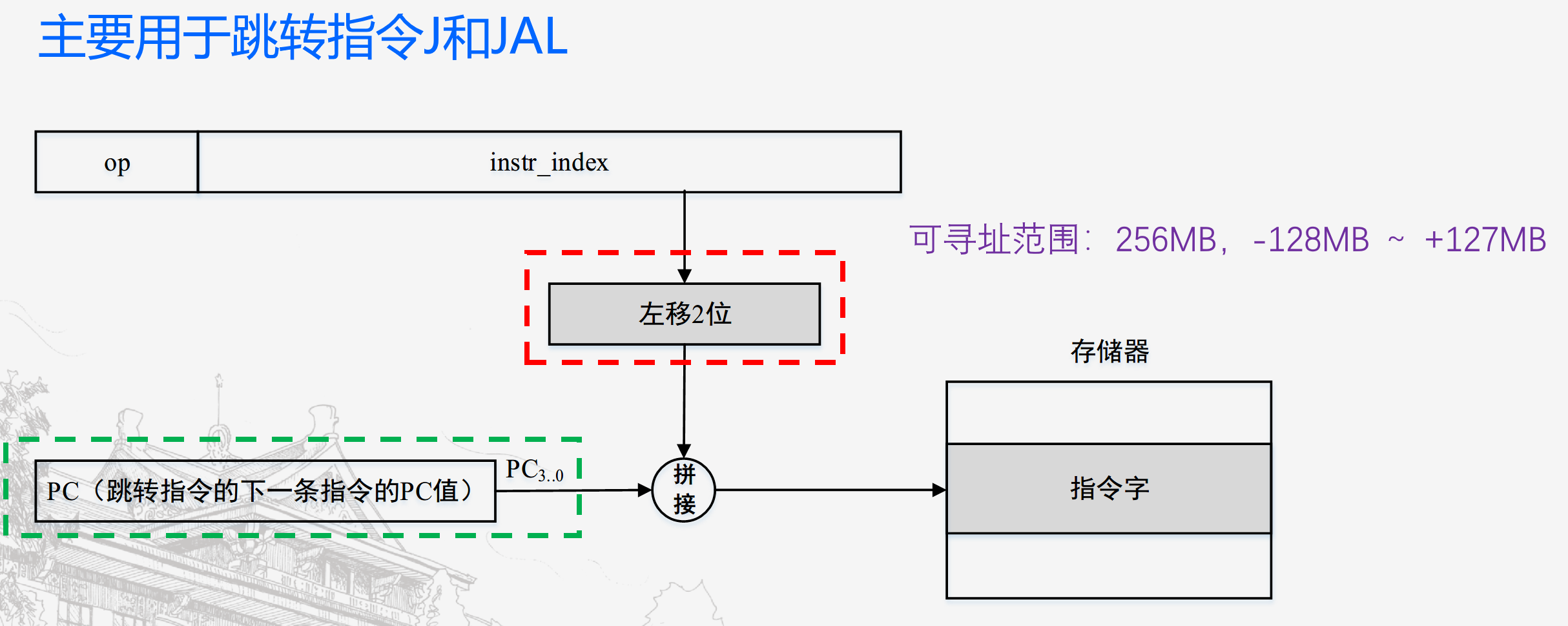

跳转指令寻址:

伪直接寻址

PC相对寻址

异常和中断

Cache映射

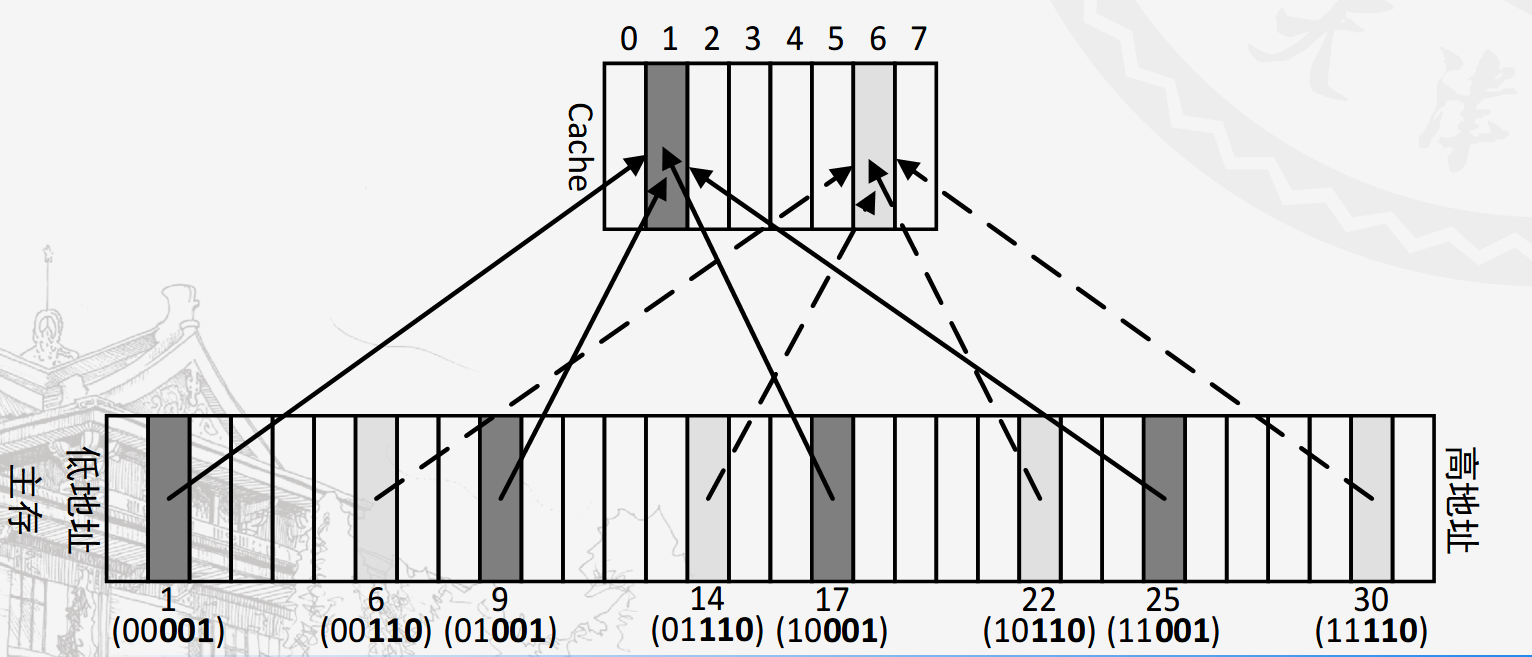

直接映射

主存中的每个块只能放在Cache中的唯一位置(行)

Cache行号=主存块号 mod Cache 行数

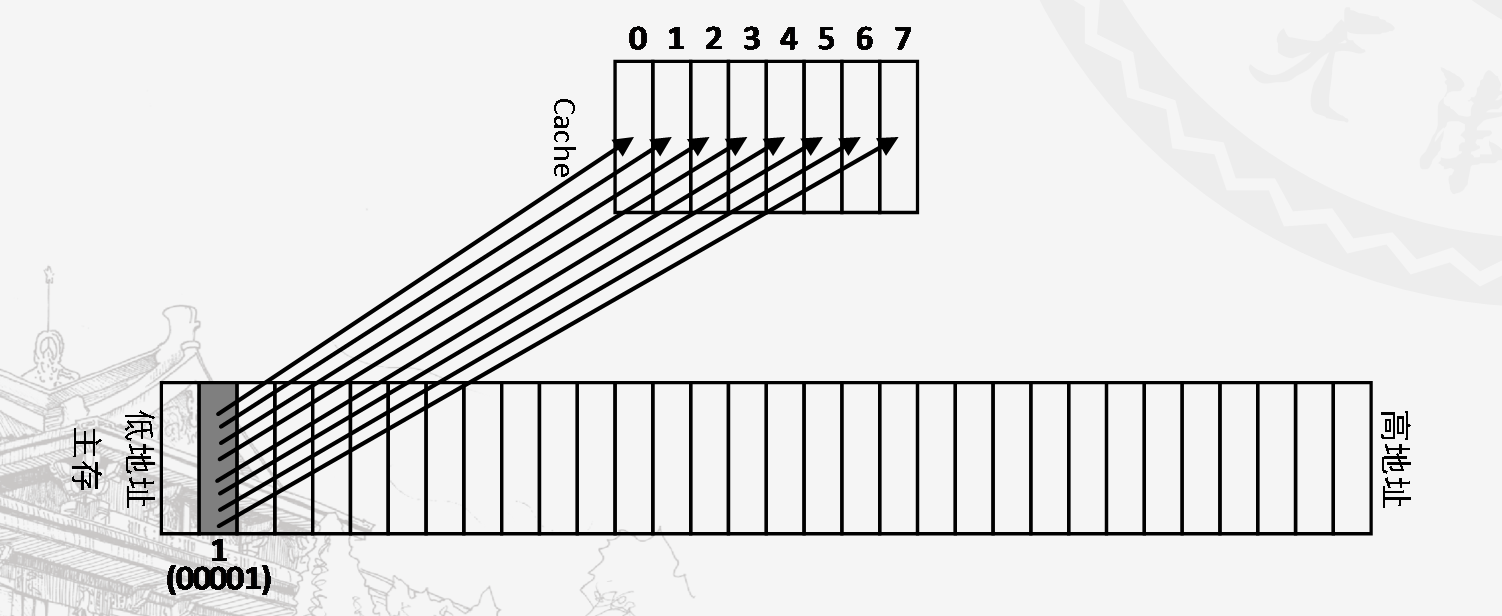

全相联映射

主存中的每个块可放置在Cache中的任何位置(行)

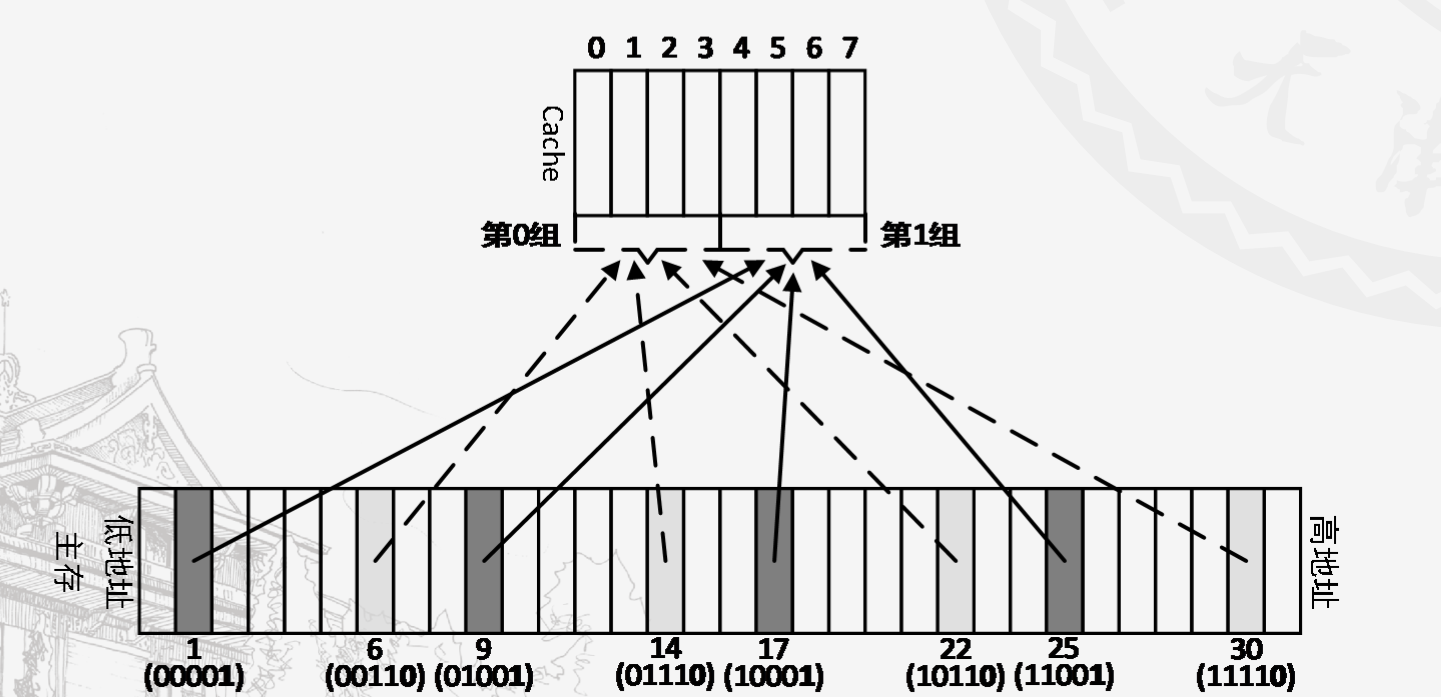

N路组相联映射

一个Set是若干块的集合

主存和Cache中的组都具有同样大小(组内块数相同)

“N路”指每个组中包含的块(行)的数目,也称为相联度

主存中的一个块首先被映射到Cache中的唯一一组中,然后该块可以放在这个组的任何一行中

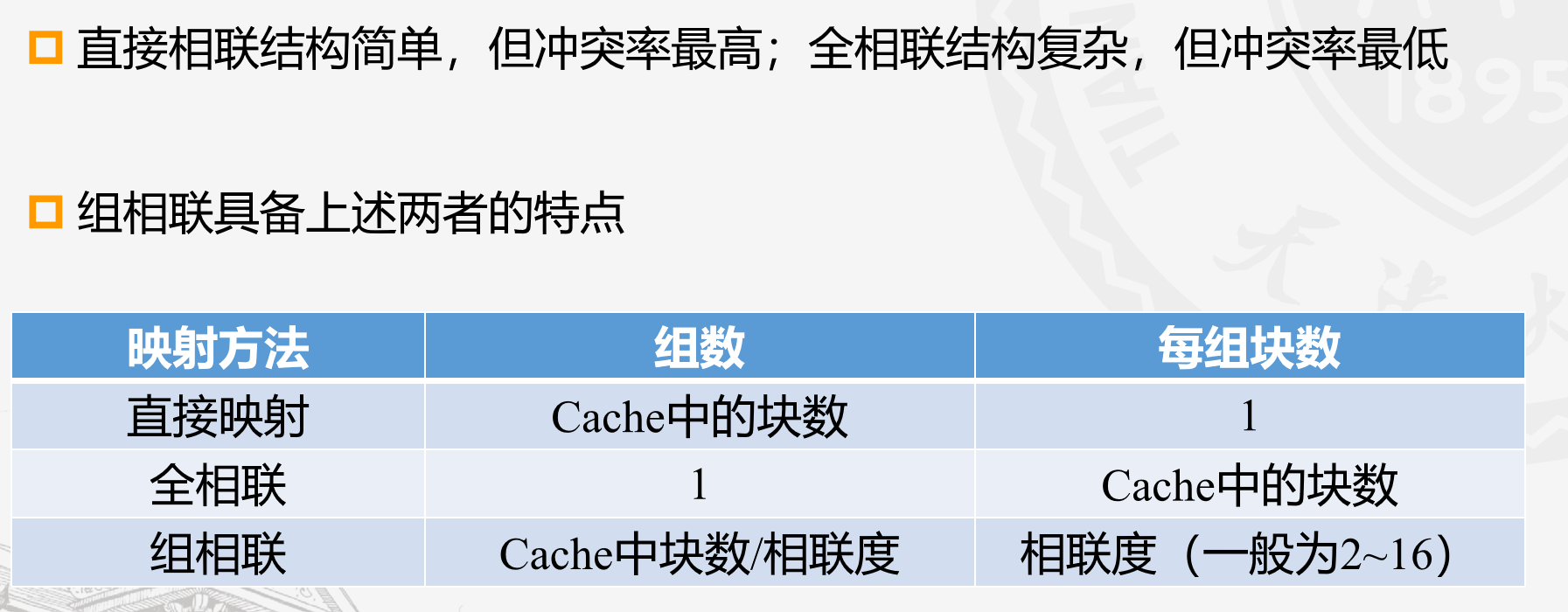

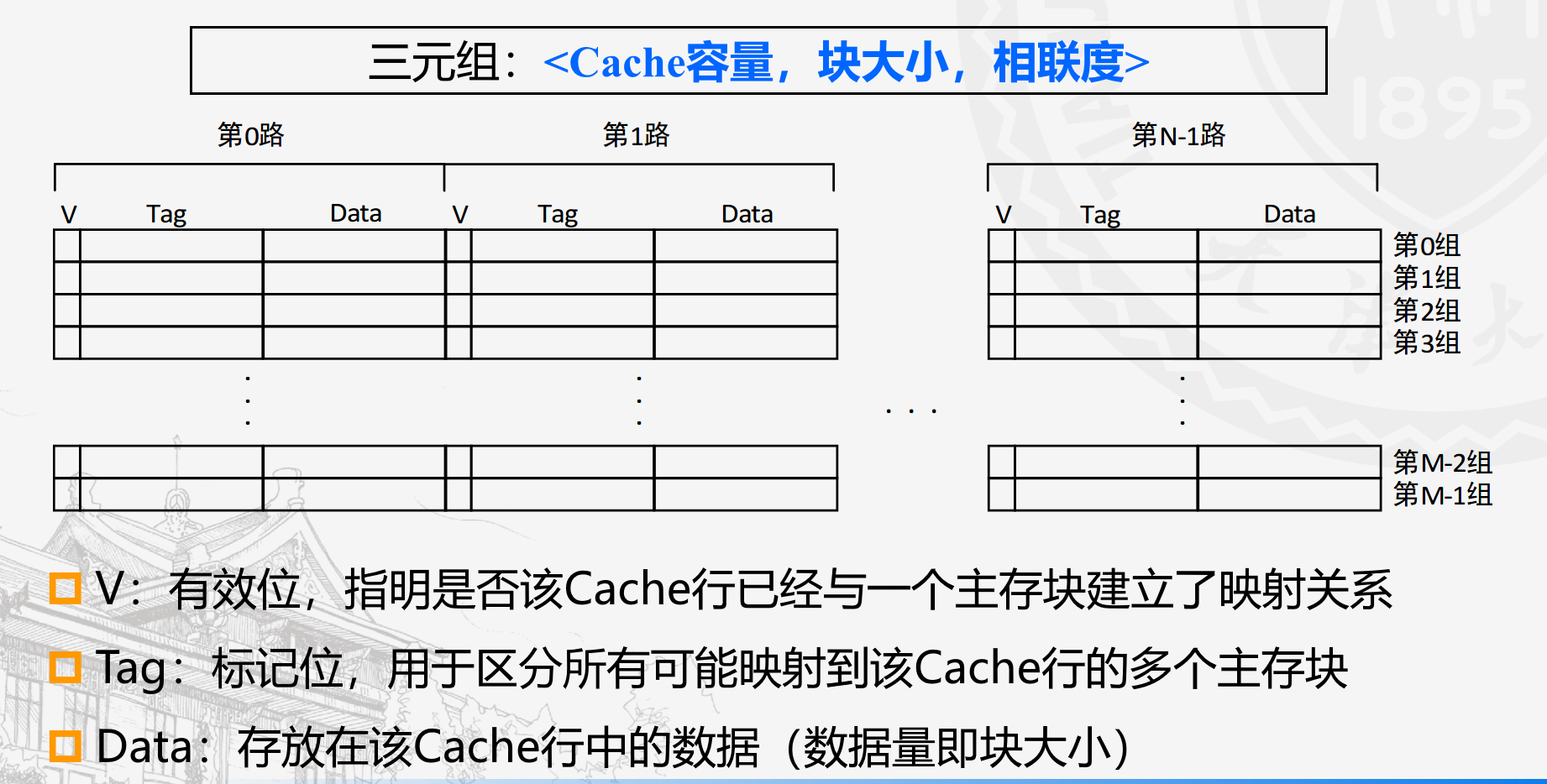

总结

Cache结构的表示

Cache块替换策略

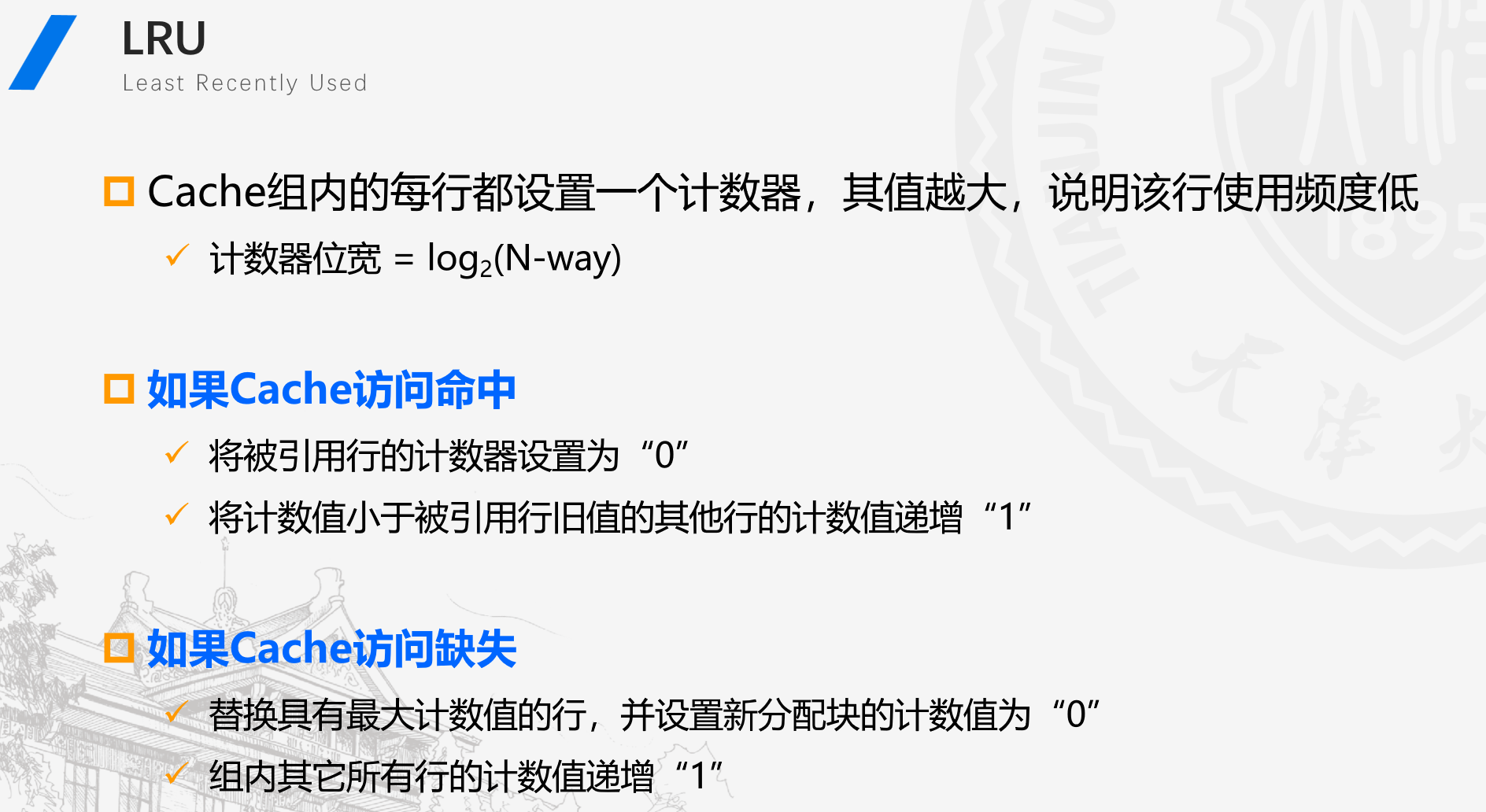

LRU

Cache写命中策略

写直达

写回

写分配

写不分配

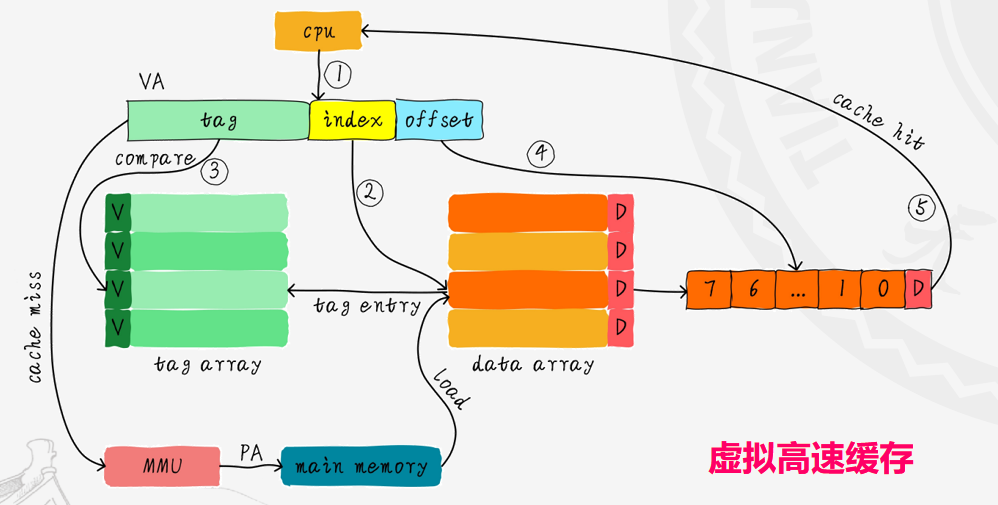

虚拟索引虚拟标记(VIVT)

优点: 不需要每次访存的时候把虚拟地址经过MMU转换为物理地址缩短了访存关键路径, 提升了频率, 提升了Cache访问速度

缺点: 即使Cache命中,也需要访问并更新TLB(两者可以并行) 进程切换需要冲刷Cache,或者增加PID(进程ID)位 歧义问题(ambiguity) 别名问题(alias)

歧义问题: 相同的虚拟地址映射到不同的物理地址 假设A进程的虚拟地址0x4000映射物理地址0x2000,B进程的虚拟地址0x4000映射物理地址0x3000。A进程切换到B进程,导致0x4000地址访问命中,而对应的是物理地址0x2000中的数据,从而出现错误 解决方案:冲刷(flush)Cache(使用专门的Cache指令,例如MIPS中的Cache),保证切换后的进程不会错误的命中上一个进程的缓存数据

别名问题: 不同的虚拟地址映射到相同的物理地址,例如进程间通信假设虚拟地址0x2000和0x4000都映射到相同的物理地址0x3000,其中虚拟地址中的[15…4]位作为index,此时同一物理地址数据被加载到不同的Cache Line,容易破坏数据一致性。

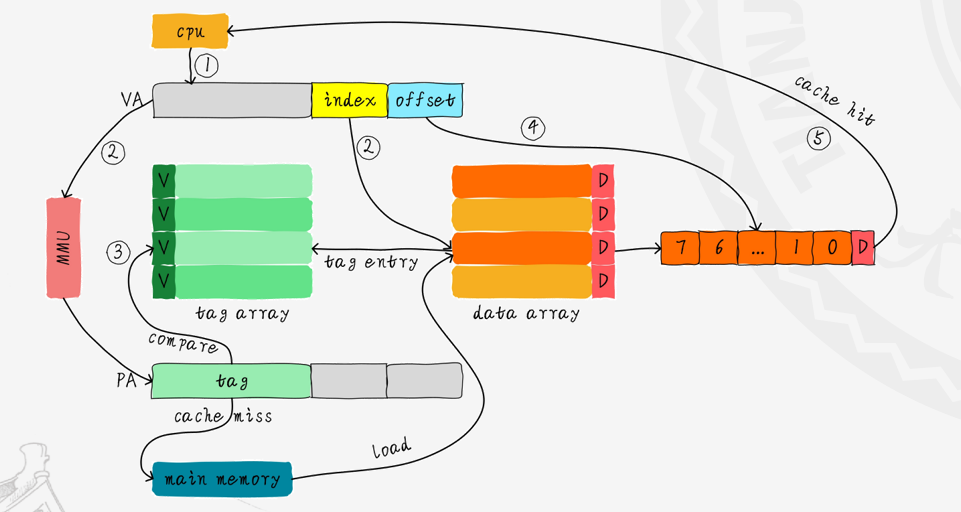

物理索引物理标记

从虚拟地址中抽取index查找Cache,从物理地址中抽取tag进行比较 Cache的查找和物理地址的转换同时进行,性能优于PIPT 不存在歧义问题,但依然存在别名问题。

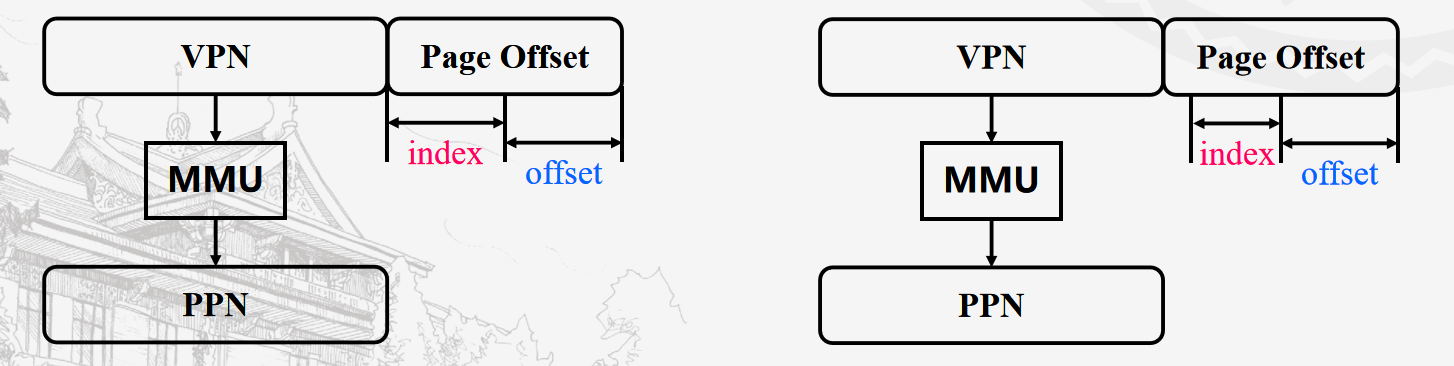

VIPT中的别名问题

直接映射:当Cache容量不大于页大小时,将不会产生别名问题 组相联:当Cache中一路的容量不大于页大小时,将不会产生别名问题 此时,index位于页偏移之中,虚拟地址和物理地址对应的index相同 VIPT相当于PIPT

解决方案1:提高相联度,将索引index控制在page offset字段范围之内 解决方案2:使用大页,将索引index控制在page offset字段范围之内 解决方案3:调整虚实映射,避免相同物理地址数据加载到不同Cache行对于直接相联,在建立共享映射的时候,虚拟地址都是按照Cache大小对齐对于组相联,在建立共享映射的时候,虚拟地址都是按照一路Cache大小对齐 解决方案4:但满足不了将索引VA的index控制在page offset字段范围之内时,需要操作系统提供支持,即Page Color功能。